光技術情報誌「ライトエッジ」No.24(2002年4月発行)

先進実装研究会「装置見学会」講演

(2001年11月)

『ポストSMT化を狙う電子部品内蔵基板技術』

場所:横浜事業所

日時:2001年11月29日

講師:昭栄ラボラトリー株式会社

取締役所長 本多進

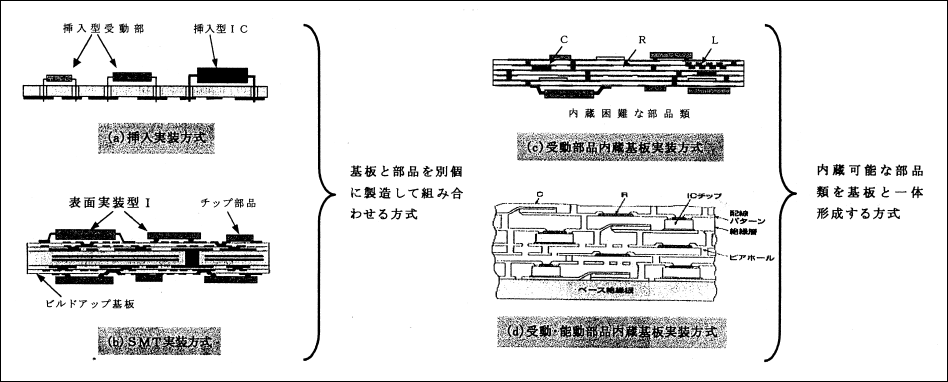

電子部品内蔵基板といっても基板やモジュールなど色々ありますが、いずれも3次元的に受動部品や能動部品を基板内に形成する方式です。これは、従来のSMT実装方式とはまったく違ってSMTの次を狙うポストSMT実装方式といえます。この方式は究極の3次元実装方式ともいえるものですが、それはこれからお話することでおわかりいただけると思います。基板と部品を別々に作っておき、基板に部品リードを挿入して裏面ではんだ付けしたり、ミニリード部品やリードレス部品を基板に表面実装するというのが従来の挿入実装方式やSMT実装方式ですが、これからお話するのは、基板の中に、配線と同時に受動部品や能動部品を入れていくという方式です(図1)。そうなると従来の基板事業というものがすっかり変わってきます。後でお話しますが、どの事業分野でこれらの製造を担当するかが難しいところです。ただ、現状では最先端の実装方式であって、すべてがこれに替わるわけではありません。それにしても今後の基板事業にかなりの変革をもたらすことになるのではないでしょうか。

図1 基板実装は挿入実装からSMT実装、受動部品内蔵基板実装、そして受動・能動部品内蔵基板実装方式へ

この方式は基板の中に入る部品は入れてしまい、どうしても入らない大容量のコンデンサや特殊な部品は外付けするというように、入る受動部品は中に入れていこうということです。それをさらに進めていくと、ICチップも中に入れてしまおうということになり、これが一番理想的な形だと思います。

従来の2次元的な実装方式から、最近では一つのパッケージに複数個のICを2~4段に積み重ねる3次元実装方式が出てきました。しかしこれらは部品レベルで作っておいて、基板の上にサーフェイスマウントで載せて行く方法ですので、従来方式の延長線上にあり、ここで述べる3次元実装方式とはかなり意味が違います。また、ASETで開発しているような、シリコンチップの中に穴をあけて上下を繋いで重ねて行こうという3次元実装方式や、さらにGaAsとSiとを常温で一体接合して3次元構造にしようとする方法なども研究されていますが、いずれもまずは部品類を3次元に作っておき、それを基板に載せていく方法です。

ここでお話する各種の部品類を基板内に入れていく方法は、色々な名前で呼ばれています。Embedded Passives、Buried Passives、Integral Passive Deviceなどです。2~3年前から米国やヨーロッパの学会ではこのようなテーマをセッションに取り上げて講演会をやっています。日本ではまだなかなか論文が集まらず難しいのですが、海外では活発化してきています。しかし、いずれにしても今のところは受動部品のみを基板内に入れていく方式が主体です。しかし私は受動部品だけを入れていって良いのかということを10年も前から言ってきました。いまやICは1チップの中に数百万個から数千万個の素子が入るようになってきて、まもなく1億個に達する時代が来ようとしています。しかし、受動部品だけを基板内に入れていっても、能動部品が入らないと中で回路が完結しないので端子の化け物になってしまいます。そこで、現状ではせいぜい数十個を内蔵するレベルにしかいかないのです。やはり能動部品も入れていかなければいけない。そこでEmbedded Passives & Activesにしないとだめです。

目下アメリカではEmbedded Passivesに注力してC、R、Lを基板内に造り込む開発を精力的に進めています。“造り込む”のであって“埋め込む”のとは違います。つまり、埋め込むというのは、C、R、Lなどのチップ部品を小さく作って基板内に埋め込んで行く方法ですが、米国ではそうではなく、中に部品を造り込んでいく方向に開発が進んでいます。

こうなってきますと、アセンブリ方式が変ってくるだけでなく、受動部品や能動部品も今の形態ではだめで、当然、基板の構造、配置・配線設計、実装設計、機器の設計などが根本的に変わってきます。基板内に回路が入っているので、設計や測定評価がシステム寄りになってきて、皆が一緒にやらなければできません。従来のように、基板は配線パターン設計だけやったものをもらって、基板メーカーが作って渡せば良いというわけにはいかなくなってきます。

なぜこのような構造が必要かといいますと、小型軽量化は勿論のこと、高性能化するICの特性を生かすために、部品端子間の配線長をできるだけ短くする必要があるからです。接続長が長いと、抵抗が生じたり、ストレーのC(寄生容量)が発生したり、ノイズの影響が出たりします。このため信号が高速になると正しく伝わらなくなってきます。結局インピーダンスのマッチングをとったり、同軸で配線すれば良いなど色々な意見が出ていますが、実際に作るのは難しく、コスト高になってしまいます。そこで、一番可能性があるのは部品端子間を最短距離で結ぶ構造をとることです。また、ファインパターンになりますと配線の引き回しで抵抗が発生しますので、それによる発熱も生じます。このためにも最短距離配線化が欠かせません。

半導体は現在デザインルールが0.13µmまできており、2~3年後には0.1µmの壁を切るだろうといわれています。しかし、そこには高い壁が立ちはだかっているのです。それは何かといいますと、0.1µm以下のファインパターンを作ることが難しいという点もありますが,ファインパターン化は70nm前後までは方法がわかってきていますので、何とかなりそうです。では何かといいますと、パターンがファインになると現在のAl配線パターンの抵抗が急激に高くなってきて、しかもファインパターン同士が接近するため、そこでストレーのCを持ち、クロストークノイズが発生して高速信号が正しく伝送されなくなってきます。また、抵抗の高いパターンに電流が流れると発熱してしまいます。今後はICチップの駆動電圧は2V、1Vあるいはそれ以下に下がる方向ですが、クロック周波数が速くなると電流を必要とし、スイッチング素子自体の発熱もさることながら配線パターンからの発熱量が大きな問題になってきます。

これらを避けるには配線導体の抵抗を下げる必要があります。これには導体パターンの引き回しを最短距離にするほか、導体に比抵抗の低い材料を使うとか、あるいは導体の厚さを厚くすることなどを考えていかないといけません。そこで高速のICチップでは、従来のAl配線を比抵抗がおよそ半分のCuのめっき配線に替え、しかも厚さをかせぐために絶縁層に溝を掘ってCu配線を埋め込んで、上部をCMP(ケミカル・メカニカル・ポリッシング)法で平坦化していくという、IBMが1997年に開発した銅ダマシン法を取り入れる方向に急速に転換が進みつつあります。

さらにICチップでは、配線距離を短くするための斜め配線や、高速信号処理に欠かせない絶縁層の低誘電率化策なども積極的に取り入れる方向で進んでいます。通常のプリント基板の絶縁層では、Low-k材といっても現状ではBCBB(Benzo Cyclo Butene:Dow Chemical)の誘電率2.7程度のものまでしか実用化されていません。しかし半導体の方は、なんと誘電率2以下を狙って有機材中に空孔(誘電率1)を入れて見かけの誘電率を下げる試みや、最近では分子構造を変えることによって空孔を入れなくても誘電率が1.9と低いものが得られたという報告も出てきています。

プリント基板でも同様のことがいえ、10µm程度のファインパターンになるとパターン形成が難しくなるだけでなく、少し引き回しただけで大きな抵抗が発生してしまい、高速信号が正しく伝送されない上に、そこに電流が流れると発熱してしまいます。そこでプリント基板の方も半導体ICに類似した考え方を導入していかなければなりません。すなわち、実装面で見るとプリント基板メーカーがやらなければならないことを半導体メーカーがすでにクリーンルームの中でやっているわけです。このため、今後は半導体プロセスに大いに学ぶ必要があります。

そういうことでなるべく配線を短くするためにEmbedded方式を採用し、まずは受動部品を入れていきましょう、次には能動部品も入れていきましょうということになるのです。

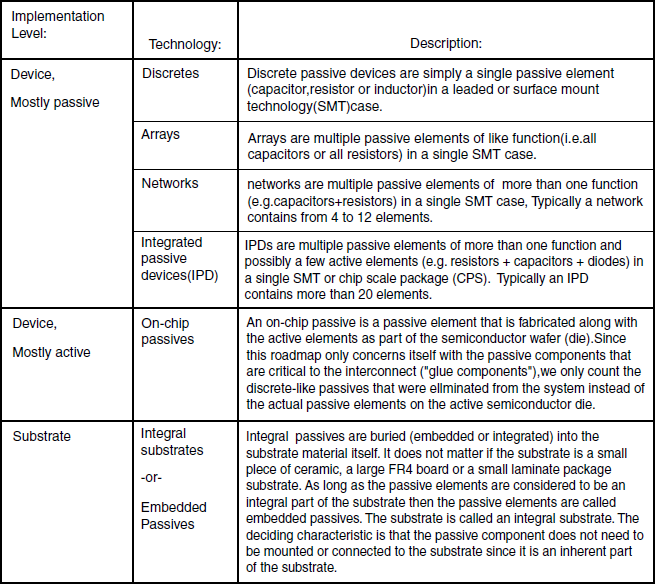

IECからは1999年と2000年に技術ドキュメントが発行され、受動部品の用語標準化(Table1)の呼びかけがあり、日本電子機械工業会(現・電子情報技術産業協会)で検討を進めています。Table1で受動部品の呼称としては、パッシブ中心で考えると、従来の単体チップ部品のほか、複数個の抵抗やコンデンサを1パッケージに入れたアレイやネットワークがありますが、新しい集積化受動部品や部品内蔵基板では、IPD(Integrated Passive Device)とかIntegrated Substrate、Embedded Passivesなどの用語を提案してきています。部品メーカーや基板メーカーはこの辺に注目する必要があるといっています。

アクティブ主体のものではOn-chip Passivesがあり、シリコンチップ上に受動部品を載せて一体化する方法が記載されていますが、半導体プロセス主体のため、この技術ドキュメントではこの表以外には触れられていません。

Table.1 Passive Component Definitions

(IEC : COMMITTEE DRAFT 40/1186/CD ; 2000-

米国は用語の標準化だけでなく部品内蔵基板の試験規格の制定などを早期に進めてイニシアティブをとろうという動きが見られますが、こうした点でも我が国は遅れをとっています。

米国ではEmbedded Passivesを主体に検討が進んでいますが、ヨーロッパではICチップも入れたEmbedded Passives & Activesを考えているようです。ただ、ヨーロッパではパッシブも作り込むのでなく、チップ部品を埋め込んでもいいのではないかという考えもあるようです。この辺は日本と似た動きです。

米国でなぜEmbedded Passivesに注力するのかといいますと、IECの技術レポートの中に受動部品の内蔵だけでも4つのメリットがあると述べられています。その一つは、基板表面は平均すると40%が受動部品で占められ、60%がICで占められているので、この40%が減っただけでも随分基板が小型化できるか、またはその分だけICが載せられるため、高密度実装が可能になるということです。さらに部品間の最短距離配線が可能になるので、回路特性がよくなります。つまりノイズが減り、スピードが上がります。また、部品の半田付け個所が減り、信頼性が向上します。もう一つはローコスト化できると強調しています。ところがヨーロッパではローコスト化のためとは言わずに、付加価値が上がるからEmbeddedPassivesに取り組むと言っています。これは視点の相違ということでしょう。

米国のNEMI(電子機器製造者協会)が2000年に発行したロードマップでは、Embedded Passivesは最短距離配線が可能で高周波特性が改善できるという点を強調しています。高速パルスでON/OFFすると、色々なノイズが出てきます。このノイズをデカップリングコンデンサで落とさなければなりません。それなのに従来の基板実装では、ICチップの周りにパッケージがあって、それを避けた場所にデカップリングコンデンサが配置されています。これでは配線が長くなってしまい性能面で好ましくありません。これに対してICバンプの直下にコンデンサを配置すれば性能が大幅に改善されると言っています。

受動部品内蔵基板にはセラミック系とポリマー系の両方があります。セラミック系は我が国が複合部品化やモジュール化でかなり先行しています。すでに携帯電話などの高周波モジュールに大量に使用されており、今後はブルートゥースにも大量採用が見込まれています。しかし、ポリマー系の製品化は遅れており、米国の方が開発で先行しています。しかしセラミック系の場合は1000°C前後の高温で焼成するので、ICチップを中に入れるというわけにはいきませんが、ポリマー系では可能になります。セラミック系ではチタン酸バリウムやフェライトのグリーンシートが得られますので、CやLは比較的容易に作り込めます。しかし一番簡単そうなRが入らないのです。何故かといいますと、Rはトリミングしなければ高精度なものが得られませんが、中に入れてしまってからではトリミングできません。しかもセラミックの場合には焼成時に15~20%程度の焼き縮みがあるので、抵抗値が狙ったところにいき難いのです。

一方、ポリマー系基板への部品内蔵はいろいろ難しい点があります。ポリマー系の場合、ビルドアップ基板の量産が進んでいるので、各層のパターンを順次作っていく段階で、部品を形成ないし埋め込んでいけばいいわけです。ポリマー系基板はセラミック系より加工時の寸法精度が良いので高精度の素子が入れやすい、低温プロセスのためエネルギーコストが安い、大型基板が作成可能なため、小型基板でもで多数個取りにすればローコスト化できるなどのメリットがあります。しかも複雑な形状の基板加工ができます。しかし最大の問題は、高誘電率材や低誘電率材、高透磁率材などのポリマー材料が入手できない点です。また、銅箔を貼らなくても、導電性の良いペーストができれば導体パターンを印刷形成できるので、そうなれば配線も内蔵部品電極も全てポリマー系で形成できます。これらのポリマー材料の開発が遅れています。

もう一つ重要な点は、セラミック系基板は1000°C前後で焼成して常温付近で使うので、非常に安定な部品が内蔵できて全体が安定しています。例えば抵抗体を入れると、ばらつきは大きいのですが、安定性はポリマー系より抜群に良いものが得られます。ところが、ポリマー系の場合は湿気がアタックしやすく、200°C以下でキュアするので、セラミック系ほど安定な抵抗は得られません。そこで、低温で安定な受動部品が形成できるような材料と加工プロセスの開発が必要になってきます。このような点からポリマー系の開発課題は多くあります。

現状ではポリマー系でコンデンサを作り込むにはどのようにするかといいますと、高誘電率のポリマーフィルムがあれば良いのですがそのようなものはないので、ポリマーに高誘電率セラミックの粉、例えばTiO2やBaTiO3の微粉末を混ぜたコンポジットフィルムの両面に電極を形成してコンデンサを作り込んでいます。もう一つ、通常の低誘電率ポリマーフィルムをベースにして、その上にポリマーが使える範囲内の温度で、スパッタやCVDで高誘電率膜を作れば、かなり大きな容量のコンデンサが入れられます。但しコスト的に高くなってしまいます。もう一つはポリマーフィルムを非常に薄くできれば、コンデンサの容量は厚さに逆比例しますので、極力薄くすればよいのですが、ピンホールや耐電圧の点で難しくなります。

コンポジットフィルムの場合は、強誘電体で3000~5000の高い誘電率を持つBaTiO3粉を樹脂の中に入れても誘電率は30~70と低くなってしまいます。ポリマーと混ぜるとこの程度に下がってしまうのです。しかしMOCVDのような方法で強誘電体薄膜を作ると、桁違いに大きなバルクに近い誘電率の膜が得られ、しかも厚さが薄くできるので大容量のコンデンサが得られます。

また、10月(2001年)に公示されたデュポン社の特許に、900°C前後の高温で焼成する厚膜をポリマー基板に形成するという方法が出ています(特開2001-160672)。つまりアルミナ基板上に印刷し、高温焼成で形成する厚膜抵抗体やコンデンサ、コイル、導体パターンなどをポリマーフィルム上に形成できるのです。どうやって形成するかといいますと、まず銅箔の上に例えば抵抗体厚膜ペーストを印刷し、銅箔のまま窒素雰囲気中で焼成します。その後それを裏返して下面銅箔とともにプリプレグに押しつけて積層します。そうすると、抵抗体が中に入った両面銅張積層板ができます。その後、銅箔をエッチングして抵抗体の電極と配線パターンを同時に形成します。これでポリマー基板上に高温で焼成した厚膜抵抗体が形成できます。ここで必要なら抵抗値をトリミングします。プリプレグを使ってこれと同様のプロセスを繰り返えせば、多層配線板の中に高温で焼成した抵抗体を複数個入れることができます。コンデンサも同様の方法で作っていきます。特性も、アルミナ基板上で焼成したものと同等のものが得られます。しかし、ポリマーの中に入れるのでどうしても湿気にアタックされがちですが、高温焼成のため非常に安定です。

また、プリント基板の中に穴を開けてチップ部品を入れていくことも、簡単なようで難しいものです。何故かといいますと、ポリマーとセラミックと膨張係数が大きく異なるものが中に入ることになるからです。基板中にSiチップを内蔵する場合も同様で、歪みの緩和策を施す必要があります。その他にも、非常に薄型のチップを作らなければなりません。

また、受動部品だけの集積回路ではなぜ多くの部品が入らないかといいますと、受動部品だけでは中で回路が完結しないからです。能動部品も入れないと回路にはなりません。ICチップはそうなっているので、数百万個の素子がシリコンチップの中に入っても端子数は多くても数百ピンですむのです。このことはIECのレポートの中にも出てきます。60個ほどの受動部品を入れても、端子が28本も必要になります。内蔵受動部品が多くなれば端子数が多くなってしまうので、せいぜい数十個止まりということになってしまいます。このような理由から、受動部品だけでなく能動部品も入れていかなければならないのです。ただし、熱応力緩和策や、放熱をどうするかという問題が出てきます。

こうした実装には半導体のテクノロジーを幅広く使っていかなければなりません。さらに実際に実行するためには、材料開発から部品や基板の構造変更、材料によるストレス緩和策、熱を逃がすのにどうするか、理想的な3次元の配置・配線はどのようにするかなどといった点についても今までとは違った考え方を導入していかなければなりません。当然、プロセスもアセンブリマシンも変わってきます。さらに測定評価、リペアをどうするかなどさまざまな課題があります。

また、こうした事業をどこでやるのかも問題です。基板メーカーか、電子部品メーカーか、基板の中にICチップを入れるのは半導体メーカーか、内容がシステムよりになってくることからアセンブリメーカーやセットメーカーも黙ってはいないでしょう。

以上述べたさまざまな課題については、エレクトロニクス実装学会で電子部品研究会内に電子部品内蔵基板分科会を作り、今後、ディスカッションや情報交換をやっていこうと動き出したところです。ご関心のおありの方は是非ともご参加ください。

セミナー風景